### **General Description**

The MAX14579E/MAX14579AE provide a simple solution for detecting the insertion and managing the operation of a 3.5mm stereo headset with a microphone. These devices integrate all circuitry required to detect SEND/ END button press events and generate required microphone bias voltages.

The devices are managed with only three GPIOs from the host controller to select between call mode and standby mode, and monitor the SEND/END and jack insertion status. In call mode, the low-noise LDO is enabled to provide DC bias to the externally preamplified microphone. In standby mode, microphone low-power pulsing is enabled to reduce supply current while waiting for a SEND/END button press event. Two open-drain outputs signal the host controller when an insertion/removal or SEND/END button press event occurs.

The MAX14579E/MAX14579AE manage jack insertion detection by monitoring a 3.5mm socket with a normally open jack insertion switch.

The devices are available in an 8-pin TDFN package, and are fully specified over the -40°C to +85°C extended temperature range.

### **Features**

- **♦ 3.5mm Jack Insertion Detection**

- ♦ Simple Interface: One Input/Two Open-Drain **Outputs**

- **♦ Low-Power Microphone Mode**

- **♦ Low-Noise, High-PSRR Microphone Bias** Generator

- ♦ Click-and-Pop Suppression

- ♦ High-ESD Protection on MIC and DETIN Inputs ±15kV Human Body Model (HBM)

**Applications**

Cell Phones

e-Readers

Tablet PCs

### **Ordering Information**

| PART             | TEMP RANGE     | PIN-PACKAGE |  |  |

|------------------|----------------|-------------|--|--|

| MAX14579EETA+    | -40°C to +85°C | 8 TDFN-EP*  |  |  |

| MAX14579AEETA+** | -40°C to +85°C | 8 TDFN-EP*  |  |  |

<sup>+</sup>Denotes a lead(Pb)-free/RoHS compliant package.

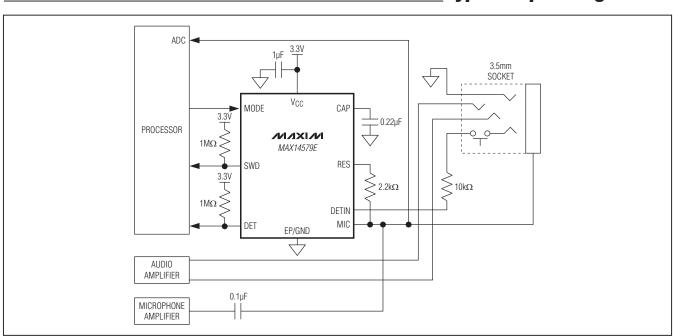

### **Typical Operating Circuit**

MIXIM

Maxim Integrated Products 1

<sup>\*</sup>EP = Exposed pad.

<sup>\*\*</sup>Future product—contact factory for availablity.

### **ABSOLUTE MAXIMUM RATINGS**

| (Voltages referenced to ground.)            | Operating Temperature Range40°C to +85°C |

|---------------------------------------------|------------------------------------------|

| VCC, MODE, SWD, DET0.3V to +6V              | Junction Temperature+150°C               |

| CAP, MIC, DETIN, RES0.3V to (VCC + 0.3V)    | Storage Temperature Range65°C to +150°C  |

| Continuous Current into Any Terminal ±100mA | Lead Temperature (soldering, 10s)+300°C  |

| Continuous Power Dissipation (TA = +70°C)   | Soldering Temperature (reflow)+260°C     |

| TDFN (derate 11.9mW/°C above +70°C)953.5mW  |                                          |

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

### PACKAGE THERMAL CHARACTERISTICS (Note 1)

TDFN

Junction-to-Ambient Thermal Resistance (θJA)......83.9°C/W Junction-to-Case Thermal Resistance (θJC)......37°C/W

**Note 1:** Package thermal resistances were obtained using the method described in JEDEC specification JESD51-7, using a four-layer board. For detailed information on package thermal considerations, refer to <a href="https://www.maxim-ic.com/thermal-tutorial">www.maxim-ic.com/thermal-tutorial</a>.

### **ELECTRICAL CHARACTERISTICS**

$(V_{CC} = 2.5V \text{ to } 5.5V, C_{DETIN} < 100pF, T_A = -40^{\circ}C \text{ to } +85^{\circ}C, \text{ unless otherwise noted.}$  Typical values are at  $V_{CC} = 3.6V, T_A = +25^{\circ}C.$ ) (Note 2)

| PARAMETER                             | SYMBOL  |                          | CONDITIONS                                           | MIN                         | TYP                         | MAX             | UNITS |

|---------------------------------------|---------|--------------------------|------------------------------------------------------|-----------------------------|-----------------------------|-----------------|-------|

| DC CHARACTERISTICS                    |         |                          |                                                      |                             |                             |                 |       |

| Supply Voltage Range                  | Vcc     |                          |                                                      | 2.5                         |                             | 5.5             | V     |

| VCC Undervoltage-Lockout<br>Threshold | VCCUVLO | VCC rising               |                                                      | 0.9                         | 1.7                         | 2.45            | V     |

|                                       |         | V <sub>C</sub> C = 2.8V  | MODE = low, DETIN = high                             |                             | 0.8                         | 1.3             | μΑ    |

| V <sub>CC</sub> Supply Current        | lcc     |                          | MODE = low, DETIN = low,<br>I <sub>MIC</sub> = 300µA |                             | 8                           | 11              |       |

|                                       |         |                          | MODE = high, DETIN = low,<br>IMIC = 300µA            |                             | 500                         | 800             |       |

| DETIN Pullup Resistance               | RDETIN  |                          |                                                      |                             | 1000                        |                 | kΩ    |

| eternal Migraphona Rica Voltaga       | \/      | MODE = low               |                                                      |                             | Vcc                         |                 | V     |

| Internal Microphone Bias Voltage      | VBIAS   | MODE = high, DETIN = low |                                                      | 2.2                         |                             | V               |       |

| MIC SEND/END Detection<br>Threshold   |         |                          |                                                      | 0.20 x<br>V <sub>BIAS</sub> | 0.22 x<br>V <sub>BIAS</sub> | 0.24 x<br>VBIAS | V     |

| DETIN Detection Threshold             |         | Falling edge             |                                                      | 1/3 x<br>VCC                | 1/2 x<br>VCC                | 2/3 x<br>Vcc    | V     |

### **ELECTRICAL CHARACTERISTICS (continued)**

$(VCC = 2.5V \text{ to } 5.5V, CDETIN < 100pF, TA = -40^{\circ}C \text{ to } +85^{\circ}C, \text{ unless otherwise noted.}$  Typical values are at  $VCC = 3.6V, TA = +25^{\circ}C.)$  (Note 2)

| PARAMETER                                         | SYMBOL              | CONDITIONS                                                                                                              |                             | MIN  | TYP  | MAX  | UNITS |

|---------------------------------------------------|---------------------|-------------------------------------------------------------------------------------------------------------------------|-----------------------------|------|------|------|-------|

| LINEAR REGULATOR (CAP)                            |                     |                                                                                                                         |                             |      |      | -    |       |

| Minimum Bypass Capacitance                        | Соит                |                                                                                                                         |                             | 0.22 |      |      | μF    |

| Output Current Limit                              | ICAP                | VCAP < VLDO                                                                                                             |                             | 4    |      | -    | mA    |

| Output Voltage                                    | V <sub>LDO</sub>    | V <sub>C</sub> C = 2.8V                                                                                                 |                             | 2.0  | 2.2  | 2.45 | V     |

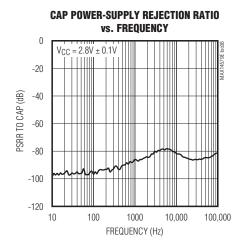

| LDO PSRR                                          | PSRR <sub>LDO</sub> | Noise from V <sub>CC</sub> to CAP, f = 217Hz,<br>V <sub>CC</sub> = 2.8V ±0.1V, I <sub>CAP</sub> = 300μA,<br>MODE = high |                             |      | 100  |      | dB    |

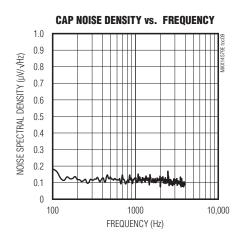

| LDO Noise                                         | NLDO                | V <sub>CC</sub> = 2.8V, I <sub>MIC</sub> = 3<br>4000Hz                                                                  | $00\mu A$ , f = 100Hz to    |      | 11   |      | μVRMS |

| LDO Turn-Off Time                                 | toff                | V <sub>CC</sub> = 2.8V, R <sub>L</sub> = 2ks 10%                                                                        |                             | 120  |      | μs   |       |

| DIGITAL SIGNALS (MODE, SWE                        | D, DET)             |                                                                                                                         |                             |      |      |      |       |

| Input-Voltage High                                | VIH                 |                                                                                                                         |                             | 1.4  |      |      | V     |

| Input-Voltage Low                                 | VIL                 |                                                                                                                         |                             |      |      | 0.4  | V     |

| Input Leakage Current                             | INLEAK              |                                                                                                                         |                             | -1   |      | +1   | μΑ    |

| Output Logic-High Leakage<br>Current (Open Drain) | IOH_LKG             | Output voltage = 5V                                                                                                     |                             |      |      | 1    | μA    |

| Output Logic-Low                                  | VoL                 | ISINK = 1mA                                                                                                             |                             |      |      | 0.4  | V     |

| DYNAMIC CHARACTERISTICS                           |                     |                                                                                                                         |                             |      |      |      |       |

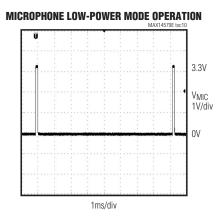

| MIC Low-Power Mode On-Time                        | tMICLPO             | $RMIC = 5k\Omega$ , $MPLP$                                                                                              |                             |      | 120  |      | μs    |

| MIC Low-Power Mode Period                         | tMICLPP             | $R_{MIC} = 5k\Omega$ , $MPLP$                                                                                           | $R_{MIC} = 5k\Omega$ , MPLP |      | 8    |      | ms    |

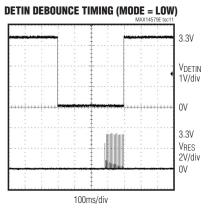

| DETIN Debounce Time                               | tDETINDEB           | E-III                                                                                                                   | MAX14579E                   |      | 300  |      | 100.0 |

| DETIN Debounce Time<br>                           |                     | Falling edge                                                                                                            | MAX14579AE                  |      | 1000 | -    | ms    |

| SEND/END Debounce Time                            | tsedeb              |                                                                                                                         |                             |      | 28   |      | ms    |

| ESD PROTECTION                                    |                     |                                                                                                                         |                             |      |      |      |       |

| MIC, DETIN                                        |                     | Human Body Model                                                                                                        |                             |      | ±15  |      | kV    |

| All Other Pins                                    |                     | Human Body Model                                                                                                        |                             |      | ±2   |      | kV    |

**Note 2:** All units are production tested at  $T_A = +25$ °C. Specifications over temperature are guaranteed by design.

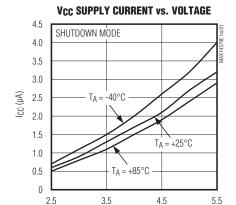

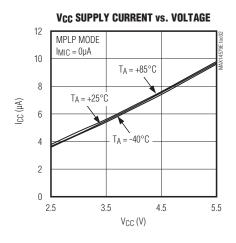

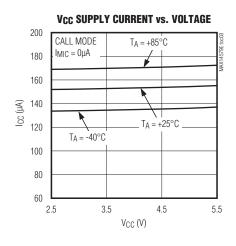

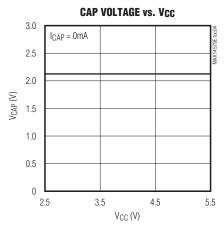

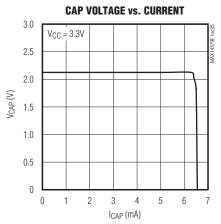

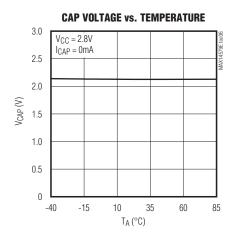

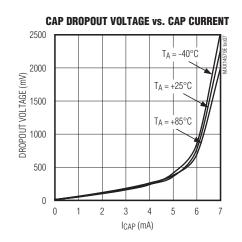

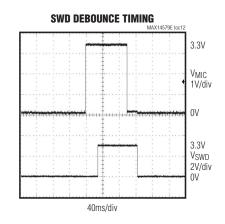

## **Typical Operating Characteristics**

(MAX14579E, VCC = 3.3V, TA = +25°C, CDETIN < 100pF, unless otherwise noted.)

$V_{CC}(V)$

## **Typical Operating Characteristics (continued)**

(MAX14579E, VCC = 3.3V, TA = +25°C, CDETIN < 100pF, unless otherwise noted.)

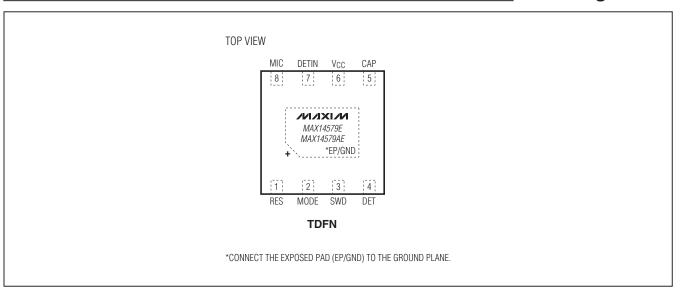

### Pin Configuration

### **Pin Description**

| PIN | NAME  | FUNCTION                                                                                                                                                                 |  |  |  |

|-----|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| 1   | RES   | Resistor Connection. Connect an external 2.2k $\Omega$ resistor from RES to MIC for microphone biasing.                                                                  |  |  |  |

| 2   | MODE  | Microphone Mode Control Input. MODE selects the operating mode. See the MODE Control Input section for more information.                                                 |  |  |  |

| 3   | SWD   | SEND/END Button Detection Output. SWD asserts when a SEND/END button press event occurs. SWD is an active-low, open-drain output.                                        |  |  |  |

| 4   | DET   | Jack Insertion Detection Open-Drain Output. DET is asserted when there is a 3.5mm jack inserted into the socket. DET is an active-low output.                            |  |  |  |

| 5   | CAP   | Internal LDO Output. Connect a 0.22µF ceramic (X5R, X7R, or better) capacitor between CAP and ground.                                                                    |  |  |  |

| 6   | Vcc   | Supply Voltage. Bypass V <sub>CC</sub> to ground with a 1µF ceramic capacitor.                                                                                           |  |  |  |

| 7   | DETIN | Jack Insertion Detection Input. An internal comparator monitors DETIN for jack insertion/removal events.                                                                 |  |  |  |

| 8   | MIC   | Microphone Connection. During audio operation, a 2.2V bias voltage is supplied to MIC through RES. An internal comparator monitors MIC for SEND/END button press events. |  |  |  |

| _   | EP    | Exposed Pad. The exposed pad is the ground connection for the device. Connect EP/GND to the ground plane.                                                                |  |  |  |

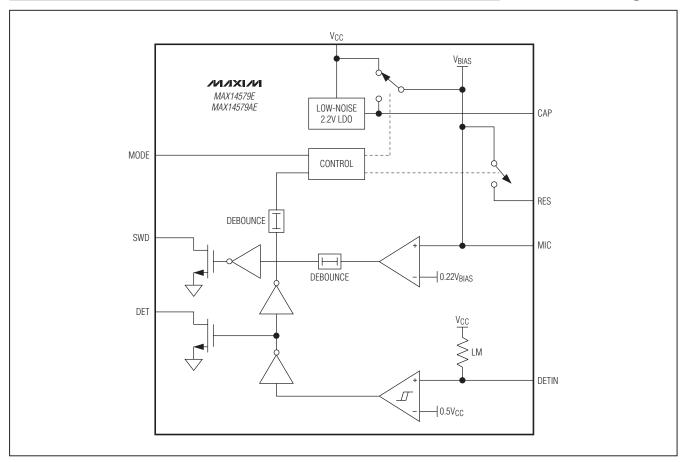

### **Functional Diagram**

### **Detailed Description**

The MAX14579E/MAX14579AE manage headsets by integrating 3.5mm jack insertion detection, microphone bias generation, and SEND/END button press detection. These devices feature a low-power microphone mode to reduce the high bias current required for microphone operation while it is not in use. The devices require only a single MODE input to select between call mode and low-power mode. See the *Jack Insertion Detection* section for details about the differences among the devices.

#### **Internal LDO Regulator**

The devices feature an internal low-noise, low-dropout regulator (LDO) for biasing the microphone connected to MIC. The LDO's output voltage is set at 2.2V. The LDO is enabled and enters low-noise mode when the MODE input is logic-high and a jack is detected. Pull the MODE input low to put the LDO in low-power shutdown mode.

### Microphone Operation and Bias Voltage Generation

An externally preamplified microphone is connected to MIC. Connect MIC to RES through an external  $2.2k\Omega$  resistor to bias the microphone.

All the devices generate a bias voltage (VBIAS) at RES. VBIAS is generated either by the internal 2.2V (typ) LDO when the MODE input is logic-high or by VCC when the MODE input is logic-low.

### **Microphone Low-Power Mode (MPLP)**

A microphone draws a large amount of current due to the required bias resistor when it is connected. This current is dissipated even while the microphone is not in use. The ICs feature internal circuitry to reduce this current while simultaneously detecting SEND/END button press events.

When microphone low-power mode (MPLP) is entered by pulling the MODE input low, the bias voltage is disconnected from the RES output and is reconnected for a short duration every 8ms (typ) to check for a SEND/END button press event. MPLP is exited when the MODE input transitions to logic-high.

Note that VBIAS is permanently disconnected from RES when no jack is inserted and microphone low-power mode is not entered.

#### **Jack Insertion Detection**

The MAX14579E/MAX14579AE detect jack insertion/ removal events by monitoring the DETIN input. Debounce circuitry ensures that transient voltages do not force the device to enter or exit MPLP due to false jack insertion/ removal detection.

#### MAX14579E Detection

The MAX14579E/MAX14579AEs' DETIN input has an internal  $1M\Omega$  pullup resistor to VCC. DETIN monitors a normally open insertion detection switch connected between DETIN and an audio line. DETIN is pulled high by the resistor, and DET is logic-high when no jack is inserted into the socket. DETIN is pulled low by the switch, and DET is logic-low when a jack is inserted.

Ensure that the total capacitance on DETIN is less than 100pF.

#### **SEND/END Button Press Detection**

The MAX14579E/MAX14579AE detect SEND/END button press events by monitoring the MIC input. A SEND/END button press is detected if the voltage at MIC falls below the MIC SEND/END detection threshold (0.22 x VBIAS (typ)) for longer than the debounce time (typ). The SWD output is logic-low for the duration of the SEND/END button press event following the debounce period. The SEND/END detection circuitry is active whenever a jack is inserted.

The debounce period built into the SEND/END button press detection allows the mechanical SEND/END button to reach steady-state before applying the microphone bias. This mitigates click-and-pop noise.

### **MODE** Control Input

An external host processor controls the MODE input. Table 1 shows the behavior of the device based on the MODE input and jack insertion status. The device enters call mode when MODE is logic-high and a jack is detected, enabling the LDO immediately in low-noise mode (LNM). The 2.2V (typ) LDO output powers VBIAS and is connected to the microphone through an external  $2.2k\Omega$  bias resistor.

Pull MODE low to put the device in standby mode. In standby mode, VCC powers VBIAS, the LDO enters shutdown mode (SDM), and the microphone bias connection either turns off permanently if no jack is inserted or enters MPLP if a jack is inserted.

The MODE input is compatible with 1.8V logic with VCC voltages up to 5.5V.

### **Applications Information**

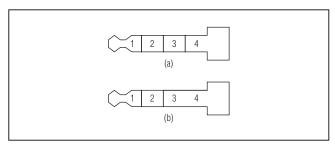

### **Typical Connections for 3.5mm Jacks**

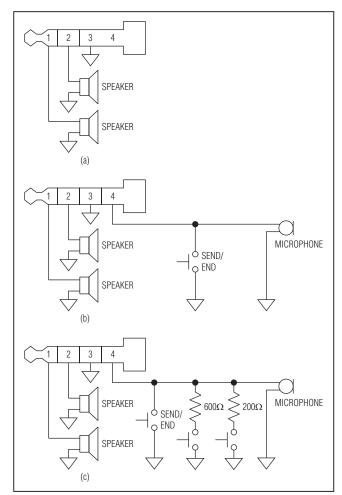

There are two typical 3.5mm jacks: tip-ring-ring-sleeve (TRRS) with four conductors (Figure 1a) and tip-ring-sleeve (TRS) with three conductors (Figure 1b). The most common configuration of the TRRS jack is to use rings 1 and 2 for audio signals, ring 3 for ground, and ring 4 for a microphone. The TRS jack typically uses rings 1 and 2 for audio signals and rings 3 and 4 as ground.

**Table 1. Operating Modes**

| MODE                  | LC   | W    | HIGH  |      |  |

|-----------------------|------|------|-------|------|--|

| DETIN/MIC<br>INSERTED | LOW  | HIGH | LOW   | HIGH |  |

| LDO Mode              | SDM  |      | SE    | M    |  |

| MIC Bias Mode         | MPLP | Off  | 2.2kΩ | Off  |  |

Figure 1. Typical 3.5mm Jacks

### **Supported Accessories**

The devices support all standard configurations of headsets with a microphone and SEND/END button on a TRS or TRRS 3.5mm jack. Figure 2 shows the supported connections of the speakers, SEND/END button, and microphone to the jack.

### Headset with No Microphone

When the 3.5mm jack in Figure 2a is inserted, the MIC input is pulled low permanently by the ground connection on the sleeve and the SWD output is logic-low permanently. This type of headset is supported by implementing a timeout period in software to recognize that the permanent logic-low is not due to a very long SEND/END button press event.

### Headset with Microphone and Normally Open SEND/END Button in Parallel

When the 3.5mm jack in Figure 2b is inserted, the MIC input is pulled below the threshold only during a SEND/END button press event. The SWD output is logic-high when the SEND/END button is pressed for more than the debounce time.

### Headset with Normally Open SEND/END Button and Resistive Remote Control

The devices support the 3.5mm jack with a microphone and two buttons in Figure 2c that is the standard Windows Mobile™ configuration. The threshold is set to detect a button press, regardless of which button is pressed.

### **High-ESD Protection**

Electrostatic discharge (ESD)-protection structures are incorporated on all pins to protect against electrostatic discharges up to ±2kV Human Body Model (HBM) encountered during handling and assembly. DETIN and MIC are further protected against ESD up to ±15kV (HBM) without damage. After an ESD event, all the devices continue to function without latchup.

Figure 2. Supported 3.5mm Accessory Configurations

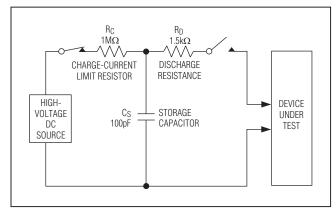

Figure 3. Human Body ESD Test Model

#### **ESD Test Conditions**

ESD performance depends on a variety of conditions. Contact Maxim for a reliability report that documents test methodology, and results.

### **Human Body Model**

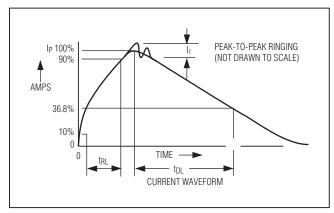

Figure 3 shows the Human Body Model. Figure 4 shows the current waveform it generates when discharged into a low impedance. This model consists of a 100pF capacitor charged to the ESD voltage of interest that is then discharged into the device through a  $1.5 \ensuremath{\mathrm{k}\Omega}$  resistor.

Figure 4. Human Body Current Waveform

### **Chip Information**

PROCESS: BICMOS

### \_Package Information

For the latest package outline information and land patterns (footprints), go to <a href="www.maxim-ic.com/packages">www.maxim-ic.com/packages</a>. Note that a "+", "#", or "-" in the package code indicates RoHS status only. Package drawings may show a different suffix character, but the drawing pertains to the package regardless of RoHS status.

| PACKAGE   | PACKAGE | OUTLINE        | LAND           |  |

|-----------|---------|----------------|----------------|--|

| TYPE      | CODE    | NO.            | PATTERN NO.    |  |

| 8 TDFN-EP | T822+2  | <u>21-0168</u> | <u>90-0065</u> |  |

### Revision History

| REVISION<br>NUMBER | REVISION DATE | DESCRIPTION     | PAGES<br>CHANGED |

|--------------------|---------------|-----------------|------------------|

| 0                  | 6/11          | Initial release | _                |

Maxim cannot assume responsibility for use of any circuitry other than circuitry entirely embodied in a Maxim product. No circuit patent licenses are implied. Maxim reserves the right to change the circuitry and specifications without notice at any time.